1.単電子転送にもとづく超低消費電力回路の研究

大規模集積回路(LSI)は微細化により集積度や性能を向上して来ましたが、寸法を縮小するほどには電源電圧が下げられなかったため消費電力密度が増大し、いまや発熱が性能を制限する状況に至っています。また携帯機器の電池寿命を長くしたり、地球環境への負荷を減らしたりするためにもLSIの消費電力低減は極めて重要です。

本研究室では、従来のLSIでは数千〜数万個の電子をひとまとまりにして扱っていたのを、電子1個1個の単位で扱うことにより回路動作に要する電力を劇的に減らすことを試みています。この様なことを可能にするデバイスは「単電子デバイス」と総称されますが、本研究室では図1(a)に示すようなシリコン(Si)の細線を横切るゲート電極を複数本もうけた単電子転送デバイスを主に扱っています。このデバイスは現行のLSIで使用されているMOSFETに似た構造を持ち、製造が容易で動作が安定で、最も実用に近いと考えられています。動作は単純で、図1(b)に示すとおり、ゲート1とゲート2を交互にon/offすることにより電子が転送されます。ゲート1と2の間に挟まれた単電子島を数10

nm程度に小さく作ることにより電子1個1個の正確な転送が可能になります。図1(c)は転送電流(I)の上層ゲート電圧やドレイン電圧に対する依存性を示しており、例えばI=ef (eは素電荷、fはゲートをon/offする周波数)となる広い領域が出現しています。このことは1周期ごとに定まった数の電子が転送されていることを示しています。

| |

|

| |

図1(a) 単電子転送デバイスの模式図、(b) 単電子転送の動作手順、(c) 転送電流(I)の上層ゲート電圧とドレイン電圧に対する依存性。単電子島を小さくすることで、転送される電子数が正確に定まるようになる。ゲートをon/offする周波数(f)に正比例する電流(I)が得られる(e: 素電荷)。[1] |

単電子転送デバイスで正確な転送を行うためには、単電子島が小さいことが重要であり、どれくらい小さいかは静電容量として定量的に評価されます。本研究室ではデバイス内部の極めて小さな容量を評価する方法も開発しています。転送デバイスの等価回路は図2(a)に示すとおりで、デバイス内部には各種の容量が存在します。これらの容量を評価するために図2(b)に示すパルス波形を各ゲートに与え、パルス電圧を様々に変えてId-Vd特性を評価することで各容量の値を導出します。図2(c), (d)のデータは150 nm技術で作製したデバイスから得たものですが、Cug=2.1 aF, Clg1=Clg2=30 aF, CΣ(中間ノード周りの総容量)=75 aFなど、aF (アト・ファラッド 10-18 F)台の微小な容量値になっていることが分りました。

| |

|

| |

図2 単電子転送デバイスにおける容量パラメーターの評価、(a)等価回路、(b)ゲートに印加するパルス波形、(c)Id-Vd依存性、(d) y切片の上層ゲートパルス振幅DVug依存性。一連の測定から、Cug=2.1 aF , CΣ=75 aF , Clg1=Clg2=30 aF等が求められる。(aF: アト・ファラッド 10-18 F) [2] |

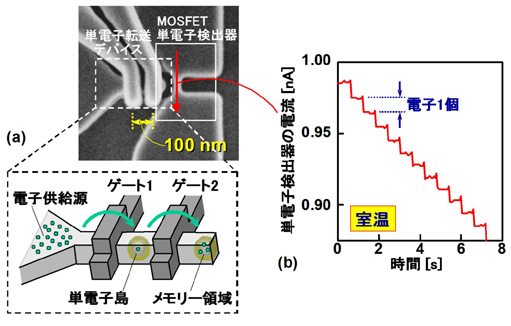

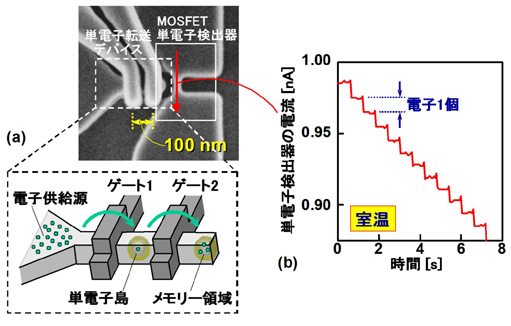

単電子転送デバイスに意味のある仕事をさせるためには、転送された電子1個1個をとらえる(検出する)必要があります。高感度に電荷をとらえる検出器(電荷計)としては、従来は単電子トランジスタが代表的でしたが、最近はデバイスの微細化とSi層を絶縁膜上に形成する(SOI: silicon on insulator)技術の進歩に伴って、MOSFETでも電子1個レベルの感度が得られるようになりました。図3(a)に、単電子転送デバイスとMOSFET単電子検出器を組み合わせた複合デバイスの例を示します。単電子転送デバイスは図1(a)のデバイスと同じものですが、ドレイン側のSi細線が途切れていて先端部が転送されて来た電子が溜まるメモリー領域になっています。このメモリー領域に近接して、縦方向に電流が流れるMOSFET単電子検出器のチャネルが配置されています。チャネルに流れるのも電子なので、メモリー領域に電子が入ると電子の流れが妨げられて電流が減少します。その結果、電子が転送されてメモリー領域に入るたびに単電子検出器の電流が階段状に減少します。

この複合デバイスは蓄えられた電子の個数を情報とするメモリー(記憶装置)として働きます。またメモリー領域に入る電子を足したり引いたり、一度に1,2,4・・・個転送したりすることにより、簡単な演算を行わせることもできます。移動する電子の個数が少なく電位差も1V程度であるため、メモリー動作や演算に伴うエネルギーは1 aJ (アト・ジュール 10-18 J)にも満たない極めて小さな値となります。

2.単電子カウンティングにもとづく超高感度光検出器の研究

従来、単一フォトン検出には光電子増倍管(PMT)やアバランシェフォトダイオード(APD)が利用されてきました。しかし、PMTは高電圧が必要、寸法が大きい(集積化しにくい)、機械的に弱い、量子効率が低い等の欠点があり、繰り返し周波数や時間分解能にも改善の余地がありました。他方、APDは単一フォトンが検出可能な程度にキャリア増倍率を上げるとダークカウント(光が入らない時の誤ったカウント)が増大する、温度や電圧の管理が煩雑、アバランシェ(雪崩増倍)のクエンチ(停止)が必要等の欠点があり、同じく繰り返し周波数や時間分解能にも改善の余地がありました。

| |

|

| |

図3(a)単電子転送デバイスとMOSFET単電子検出器を組み合わせた複合デバイス、(b) 単電子の転送に伴うMOSFET単電子検出器電流の変化。[3] |

本研究室では、既に述べたとおり微細なSOI MOSFETが電子1個を検出できるほど高感度な電荷検出器になることを利用して、光照射によって発生したキャリア(電子もしくはホール)を増倍せずに直接検出する新しいタイプの単一フォトン検出器を開発しています(図4)。低い電圧で動作させ、デバイスの大きさをナノメータ寸法とするためダークカウントは大幅に減少します。SOIを利用し、ナノメータ寸法化するため高い電荷検出感度と動作速度(繰り返し周波数)が達成されます。この結果、APDの特性を凌駕し、固体デバイスの特徴(低電圧動作、小型で集積化可能、機械的に強い等)が発揮できる単一フォトン検出器が得られます。

デバイスのナノメータ寸法化によって生じる光吸収効率の低下は、表面プラズモンアンテナの導入により対処します。表面プラズモンアンテナにより光吸収効率が増大するだけでなく、波長フィルタや偏光フィルタなどの新機能も実現できます(図5)。

| |

|

| |

図4 単電子カウンティングにもとづく超高感度光検出器の模式図。

|

| |

|

| |

図5 表面プラズモンアンテナの特性。光吸収効率を1桁程度改善でき、分光特性も自由に変えられる。[4]

|

3.グラファイト・トランジスタの研究

グラファイト(黒鉛)は炭素原子が亀の甲状に配列したシート(グラフェン)が積層した半金属結晶で、抵抗率が50 μWcm程度と低く電界効果を利用して伝導度を変調する(トランジスタ動作させる)ことは不可能と思われて来ました。ところが最近、数原子層のグラフェンを取り出して特性を測る技術が考案され、特異なバンド構造にもとづく量子ホール効果や極めて高いキャリアの移動度(室温で10,000 cm2/Vs以上)などが実験的に観測できるようになりました。しかし現状では得られるグラフェンのサイズは100 μm程度にとどまっており、優れた物性を電子デイバスとして実用化する道筋は明瞭ではありません。

本研究室ではグラフェンの電子デバイスへの応用を目指して、大面積な薄膜を得る方法を検討しています。一例が電子サイクロトロン共鳴(ECR)プラズマを利用したスパッタリング法で、グラファイト的なsp2結合を多く含む薄膜が室温で得られます。宙吊りマスクを組み込んだ基板に対して、この薄膜の堆積と斜め蒸着による金属電極形成を順次行うと、電界効果トランジスタが簡単に作製できます(図6)。薄膜の端部においては図7に示すような両極性電界効果が観測され、294 Kで2, 150 Kで7の電流オン・オフ比を達成しました。

| |

|

| |

図6 グラファイト電界効果トランジスタの構造と作製手順

|

| |

|

| |

図7 グラファイト電界効果トランジスタのドレイン電流・ゲート電圧特性。明瞭な両極性電界効果が観測され、294 Kで 2, 150 Kで 7の電流オン・オフ比が得られた。[5]

|

参考文献

[ 1 ] A. Fujiwara, et al., Appl. Phys. Lett. 84 (2004) 1323.

[ 2 ] H. Inokawa, et al., 2007 Int. Conf. Solid State Devices and Materials (SSDM) p. 874.

[ 3 ] K. Nishiguchi, et al., 2004 International Electron Devices Meeting (IEDM) p. 199.

[ 4 ] H. Satoh, et al., 2008 Int. Conf. Solid State Devices and Materials (SSDM) p. 286.

[ 5 ] H. Inokawa, et al., Jpn. J. Appl. Phys. 46 (2007) 2615. |